# Using Patent Portfolio and Filing Trend Analytics to Help Guide Patent Portfolio Development

April 5, 2016

#### Presenter

- Thomas Marlow, President, Black Hills Renewals, LLC, formerly...

- IP Director at Fairchild Semiconductor

- Co-Chair, Patent Portfolio Management & Analytics SLW

## Analytics To Drive Portfolio Development

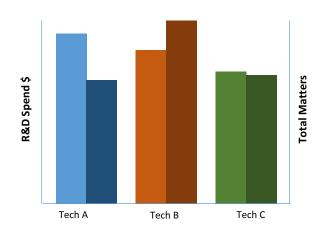

Internal

External

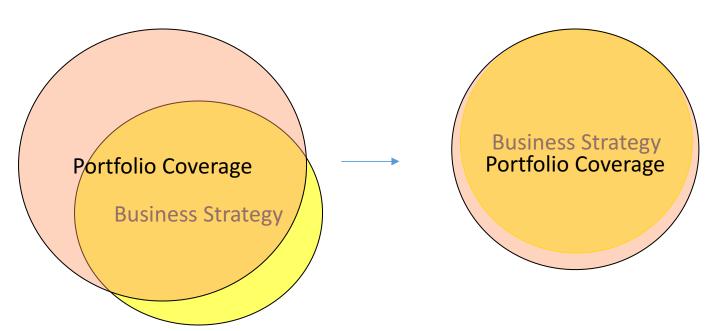

#### Internal Analysis

Portfolio Analysis

Develop and align the patent portfolio with business data &

strategy

#### **Business Alignment**

- Technology Segment Mapping

- Product Line Mapping

- Track and align patent portfolio growth along these lines to projections.

- o Filings, Renewals, Prosecution Vigilance

### Business Alignment - Geogaphy

- Key sales/end markets for products

- Key competitor manufacturing locations

- Overlay international coverage

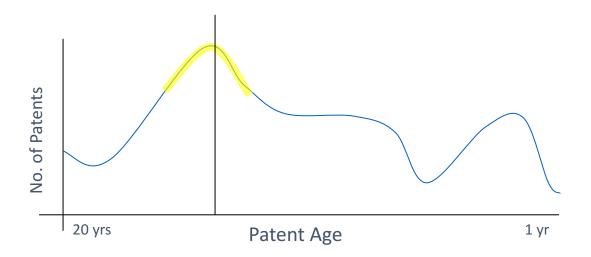

### **Business Alignment - Temporal**

Temporal Analysis – Patent ageing

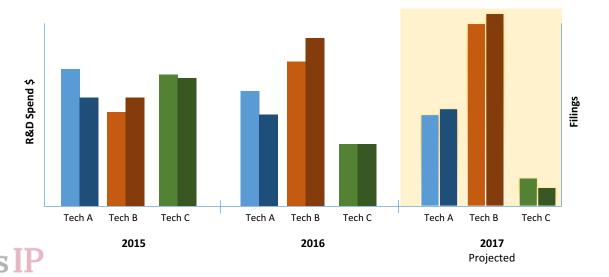

#### **External Analysis**

- Competitor & Landscape Analysis

- Trends

- Spend

- o Terms

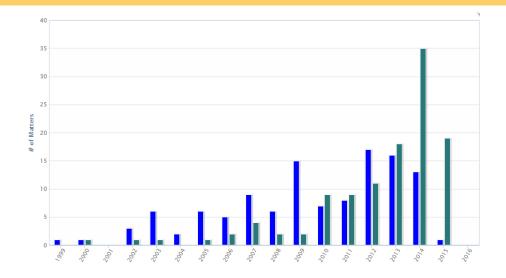

#### **Competitor Trends**

- Useful

- o Technology over time

- Country coverage (by tech if you can)

Maybe NotTiming

| COUNTRY | BAR GRAPH | MATTERS |

|---------|-----------|---------|

| US      |           | 116     |

| EP      |           | 40      |

| AU      |           | 32      |

| JP      |           | 29      |

| CA      |           | 22      |

#### **Competitor Trends**

- Useful

- Families

- > Horizontal & Vertical data

- Maybe/Maybe Not

- Longevity

- Inventors

#### **Importance**

| CALCULATED RATING •-•-• |         |                   |             |  |

|-------------------------|---------|-------------------|-------------|--|

| US Family Size          | •-0-0-0 | Non-US Coverage   | 0-0-0-0     |  |

| Patent Longevity        | 0-0-0-0 | Forward Citations | <b>•-•-</b> |  |

#### **Competitor Focus**

- Use analytics to terms replicate in some embodiments and some claims

- Key technologies apply developed technology to these discuss in invention review and IP brainstorming sessions.

conductivity type. Instead, a preferred breakdown shielding region 117 of second conductivity type (e.g., P-type) is provided. The breakdown shielding region 117 may be formed at the same time the base region 116 is formed, for example. However, as illustrated best by FIG. 6 which is a cross-sectional view of an integrated power semiconductor device 300' according to a third embodiment of the present invention, the breakdown shielding region 117 may also be formed deeper (and more highly doped) than the base region 116 to further increase the likelihood that avalanche breakdown will occur in the transition mesa region instead of within the active region. The use of breakdown shielding regions to improve the breakdown characteristics of power semiconductor devices is also described in commonly 1998, entitled "Rugged Schottky Barrier Rectifiers Having Improved Avalanche Breakdown Characteristics", the disclosure of which is hereby incorporated herein by reference.

Numerical simulations of the unit cell 300 of FIG. 5 were performed using a drift region doping concentration which 20 increased from a value of 1×10<sup>16</sup> cm<sup>-3</sup> at a depth of 1 micron to a value of  $2\times10^{17}~{\rm cm}^{-3}$  at a trench depth (T<sub>D</sub>) of 5 microns. The thin portion of the gate electrode insulating region 124 had a thickness of 500 Å, the thick portion of the gate electrode insulating region 124 had a thickness of 3000 Å and the first field plate insulating region 134 had a uniform thickness of 3000 Å. Based on these parameters, the simulated potential contours were shown to be uniformly spaced in both the active and termination regions. The simulated current flowlines also indicated that breakdown would occur simultaneously in both the active and termination regions so long as the breakdown shielding region 117 is electrically connected to the source electrode 128b. Accordingly, breakdown in the integrated power device 300 of FIG. 5 is not expected to be edge limited. Moreover, in applications 3. where the GD-MOSFET unit cells in the active region are expected to be frequently driven into avalanche breakdown, it is preferable to move the location of avalanche breakdown to the more highly doped and deeper breakdown shielding region 117' within the device 300' of FIG. 6. In particular, by increasing the depth of the breakdown shielding region 117', the breakdown voltage can be decreased to a level which will provide sufficient protection to the unit cells in the active device area and improve the lifetime and reliability of hereinbelow with respect to FIG. 7, the breakdown voltage and the specific on-resistance R<sub>sp,on</sub> can also be scaled downward by decreasing the epitaxial layer thickness of the drift region 112.

which extends all the way to the Schottky rectifying junction at the face, a uniformly doped region extends adjacent the Schottky rectifying junction in the modified TMBS rectifier of FIG. 7. As illustrated, this uniformly doped portion of the drift region has a doping concentration of 1×1016 cm-3 therein. The advantages of including a uniformly doped region adjacent the Schottky rectifying junction in a TMBS device are more fully described in the aforementioned application entitled "Rugged Schottky Barrier Rectifiers Having Improved Avalanche Breakdown Characteristics".

This hybrid power device 400 is designed so that the GD-MOSFET unit cells have very low specific on-state resistance, the modified TMBS structure has very low leakage current and low on-state voltage drop and the combined assigned U.S. application Ser. No. 09/167,298, filed Oct. 6, 15 hybrid structure exhibits very low parasitic inductance. In particular, simulations of the hybrid device of FIG. 7 illustrate that the on-state voltage drop of both the GD-MOSFET and modified TMBS are reduced because of improved current spreading in the N+ substrate region 114. The specific on-resistance R<sub>sn,on</sub> can also be scaled downward by decreasing the epitaxial layer thickness of the drift region 112. This reduction in epitaxial layer thickness causes the non-rectifying junction formed between the drift region 112 and the drain region 114' (illustrated by the dotted line in FIG. 7) to move up along the sidewalls of each trench, without any other modification in the process. Accordingly, the reduction in epitaxial layer thickness (or increase in trench depth) results in the formation of an interface between the bottom of the trench 120b and the drain region 114'. The simulations also indicate the possibility of higher temperature operation with smaller heat sinks because of an improvement in the leakage current characteristics. The hybrid device also limits the amount of parasitic inductance between the GD-MOSFET and modified TMBS rectifiers

As further illustrated by FIG. 7, an increase in the depth of the base region 116 to the level illustrated by the dotted line 116 can also be used advantageously to suppress the degree of any impact ionization near the gate insulating region 124 which may arise in response to hot electron injection during avalanche breakdown. In particular, steps to form the gate insulating region so that there is an overlap between the thick portion of the gate insulating region 124 (extending upward from the bottom of the trench) and the the overall device 300'. In addition, as described more fully 45 base region 116 can be used to enhance the electric field contours at the corner of the gate between the thick and thin portions and thereby shield the gate insulating region from the effects of hot electron induced instabilities during avalanche breakdown. Accordingly, the gate insulating region